2: CPU architecture

Categories: Programming system

Tags: System

Before we start

As transistor density increases, clock cycle increases. Increased clock cycle does leads to faster CPU however there is more factors to it. A faster CPU requires

1️⃣ Faster clock cycle as well as

2️⃣ smaller Cycle Per Instruction(CPI).

History

1961 : first commercially-available integrated circuits created by Fairchild Semiconductor and Texas Instruments.

1965: Gordon Moore’s(director of Fairchild research) observation which says that number of transistors on chips was doubling every two years.

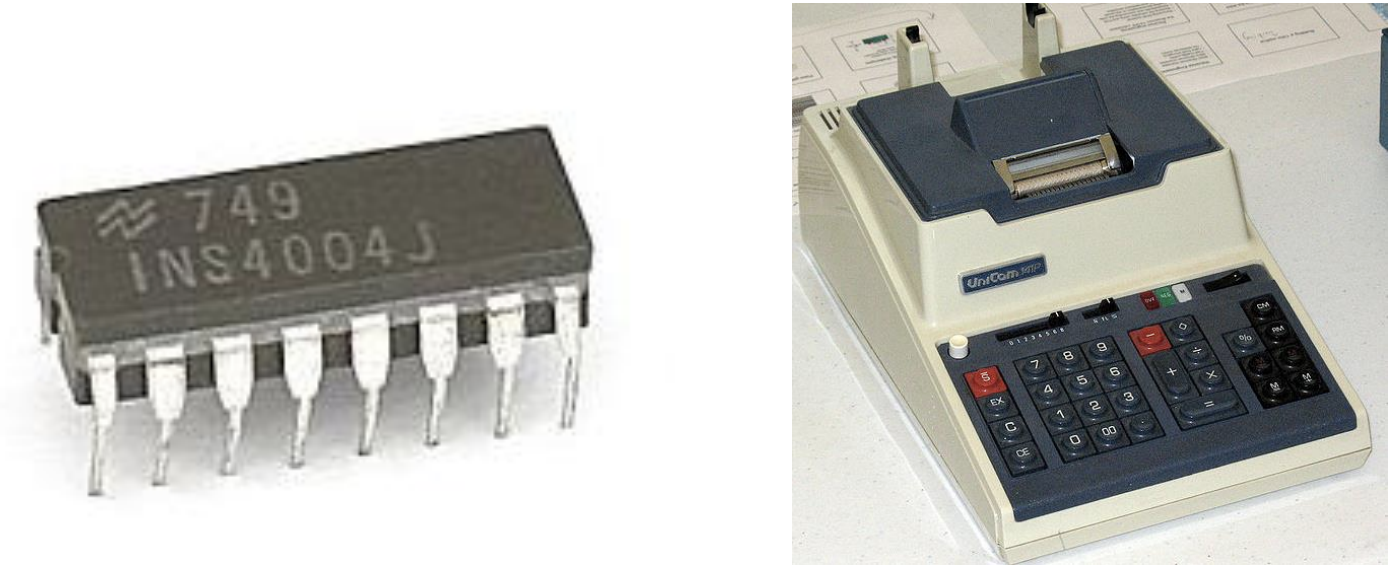

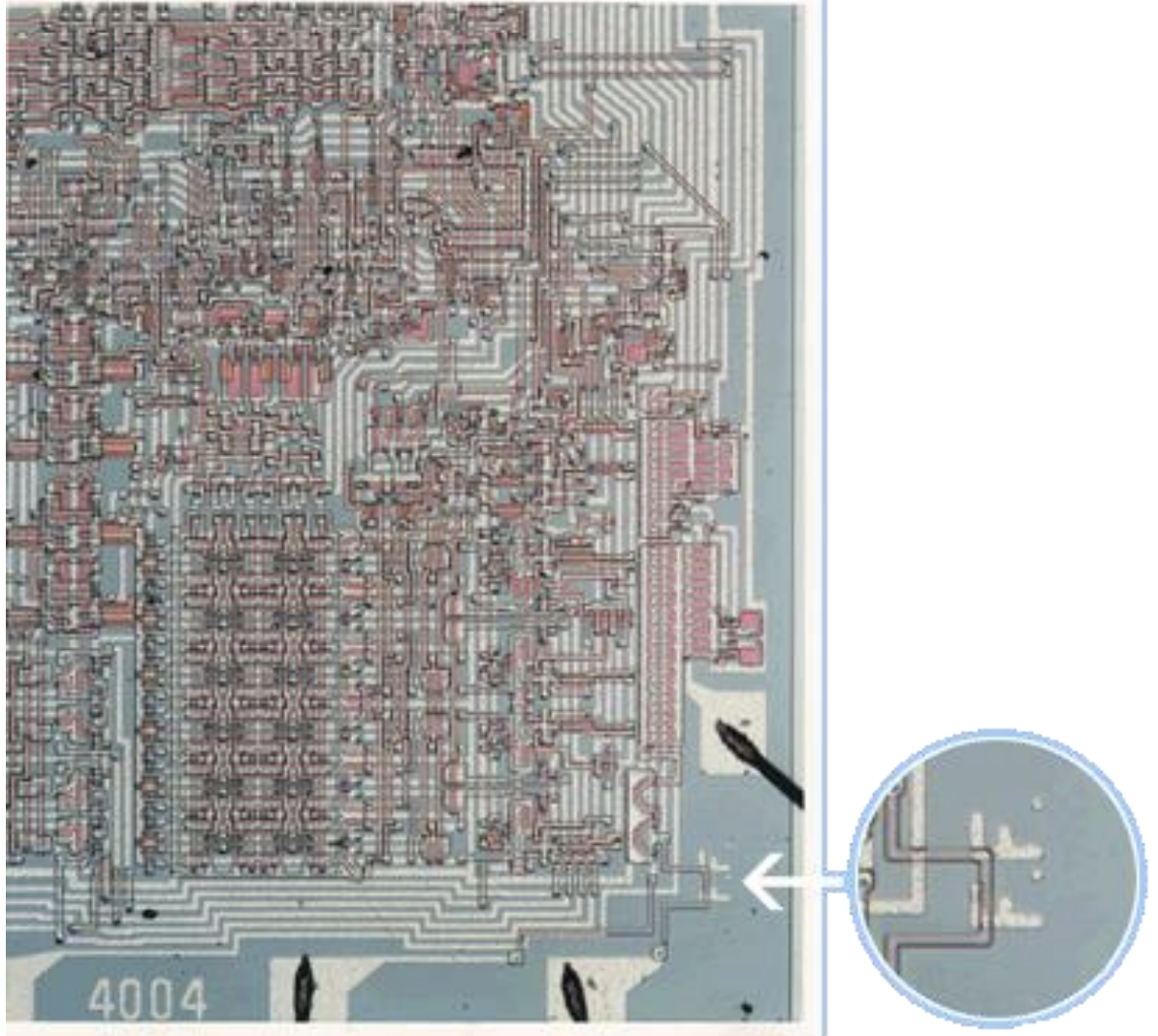

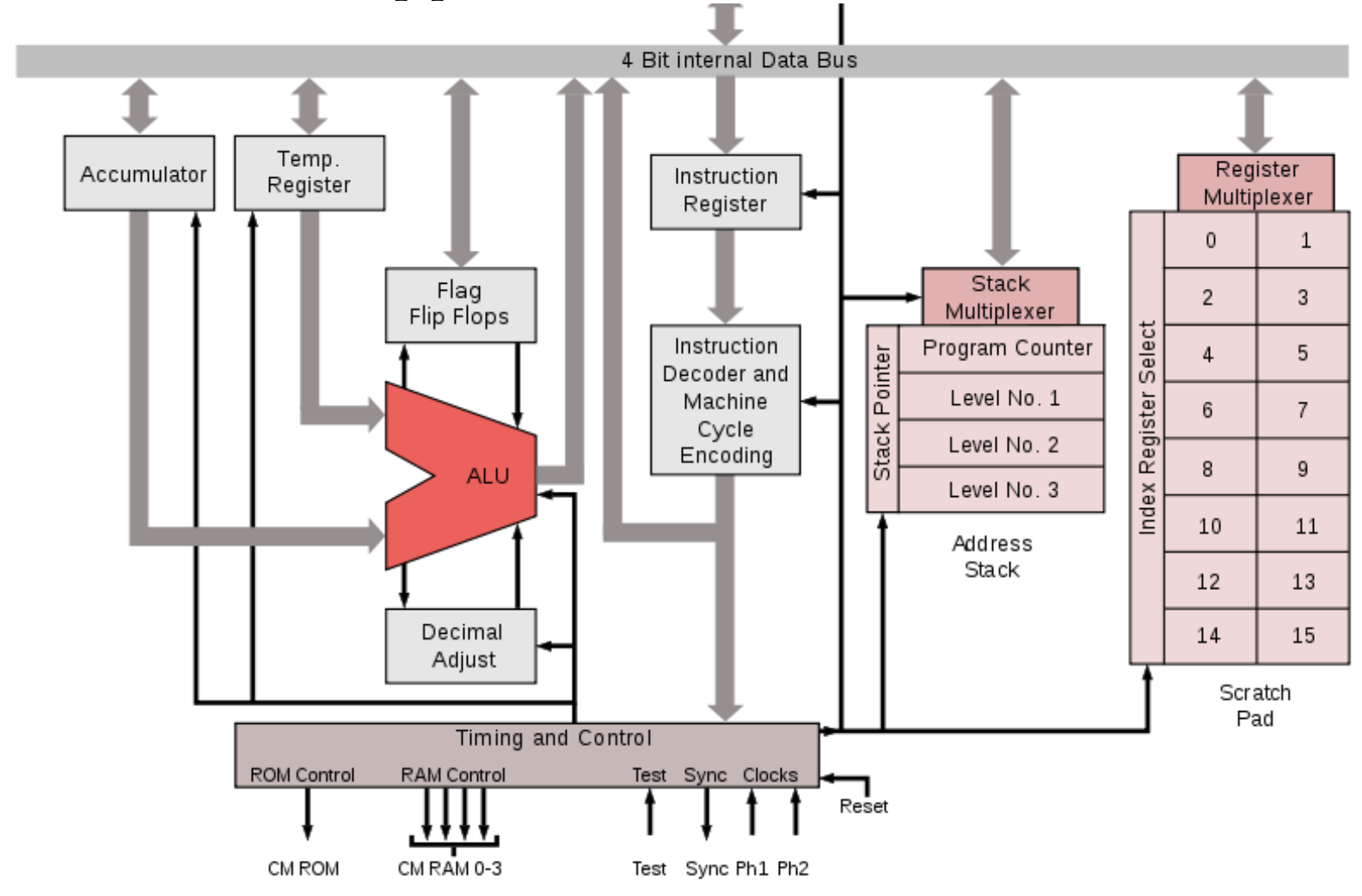

1971: Intel Releases the 4004

- First commercially available, stand-alone microprocessor(4-bit processor; 108KHz; 2300 transistors) used in calculators

- 4 chips: 4004 CPU, 4001 ROM, 4002 RAM, I/O registers

- No Virtual Memory support, No Interrupt, No pipeline

1970’s: : Increased Integration

- 4004: 4-bit processor for use in calculators

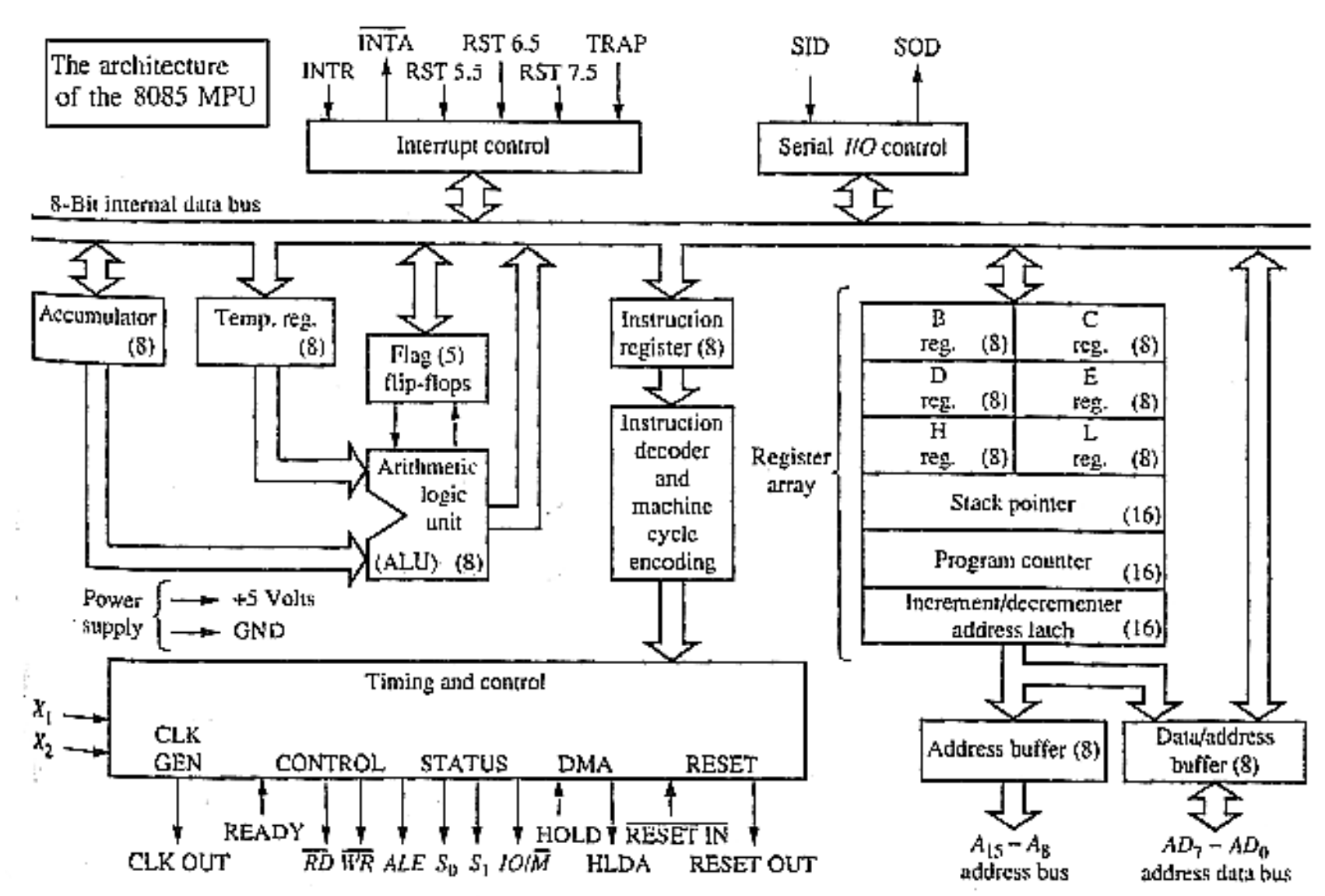

- 8008: 8-bit general-purpose processor

- 8080: 16-bit addr space, 8-bit registers, used in ‘Altair’

- 8086: Full 16-bit processor, start of x86

1980’s: RISC and Pipelining

- 1980: Patterson (Berkeley) suggest the term RISC

- RISC design simplifies implementation:

- Small number of instruction formats

- Simple instruction processing

- RISC leads naturally to pipelined implementation

- Partition activities into stages

- Each stage has simple computation

- RISC design simplifies implementation:

- 1981: Hennessy (Stanford) develops MIPS

- 1982: Makes RISC-I pipelined processors with only 32 instructions.

- 1984: Forms MIPS computers

- 1985: Pipelining: Intel 386

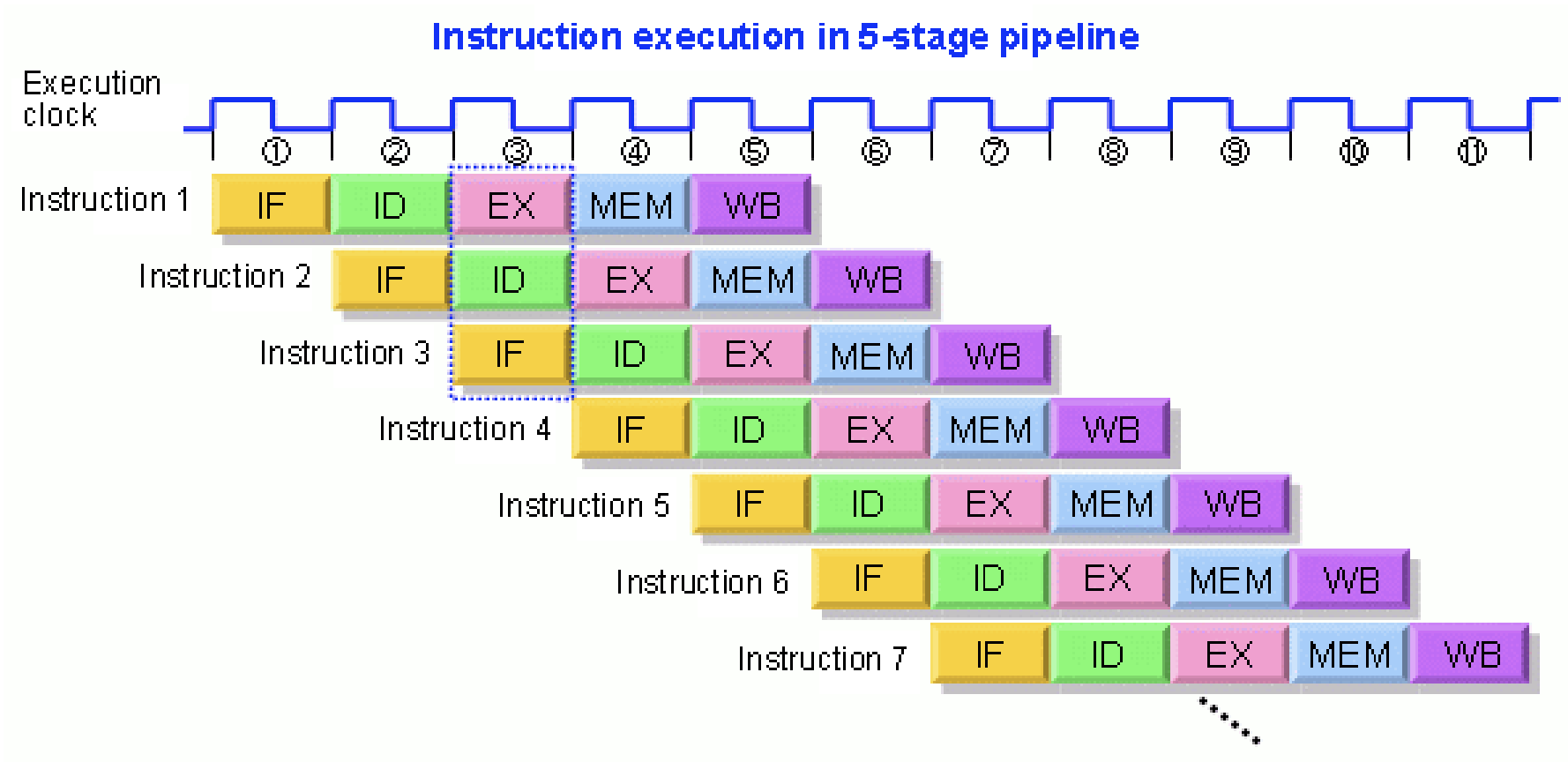

RISC(Reduced Instruction Set Computer) Pipeline.

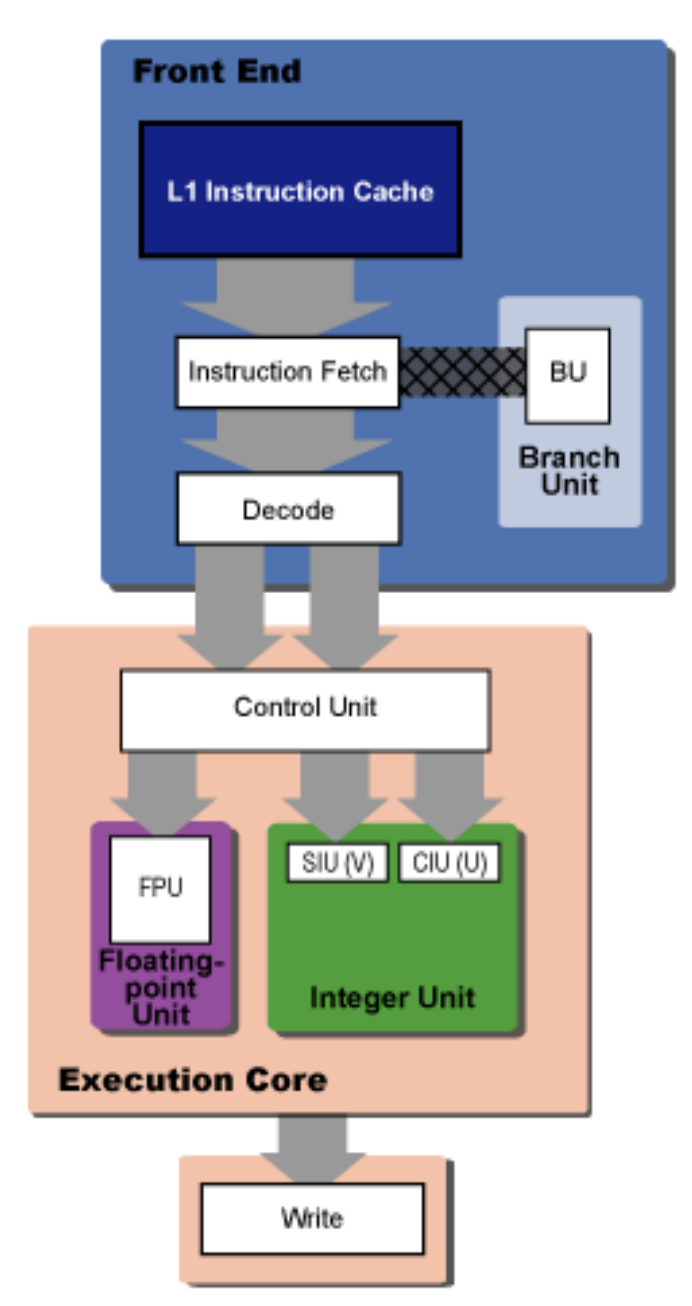

RISC, having total 5 different instructions, was designed to execute one instruction per cycle. 5 different instructions are Fetch, Decode, Execute, Memory, Write. Through pipelining, each of the instruction could be fetch after one another, reducing CPI from 5 to 1.

RISC, having total 5 different instructions, was designed to execute one instruction per cycle. 5 different instructions are Fetch, Decode, Execute, Memory, Write. Through pipelining, each of the instruction could be fetch after one another, reducing CPI from 5 to 1.

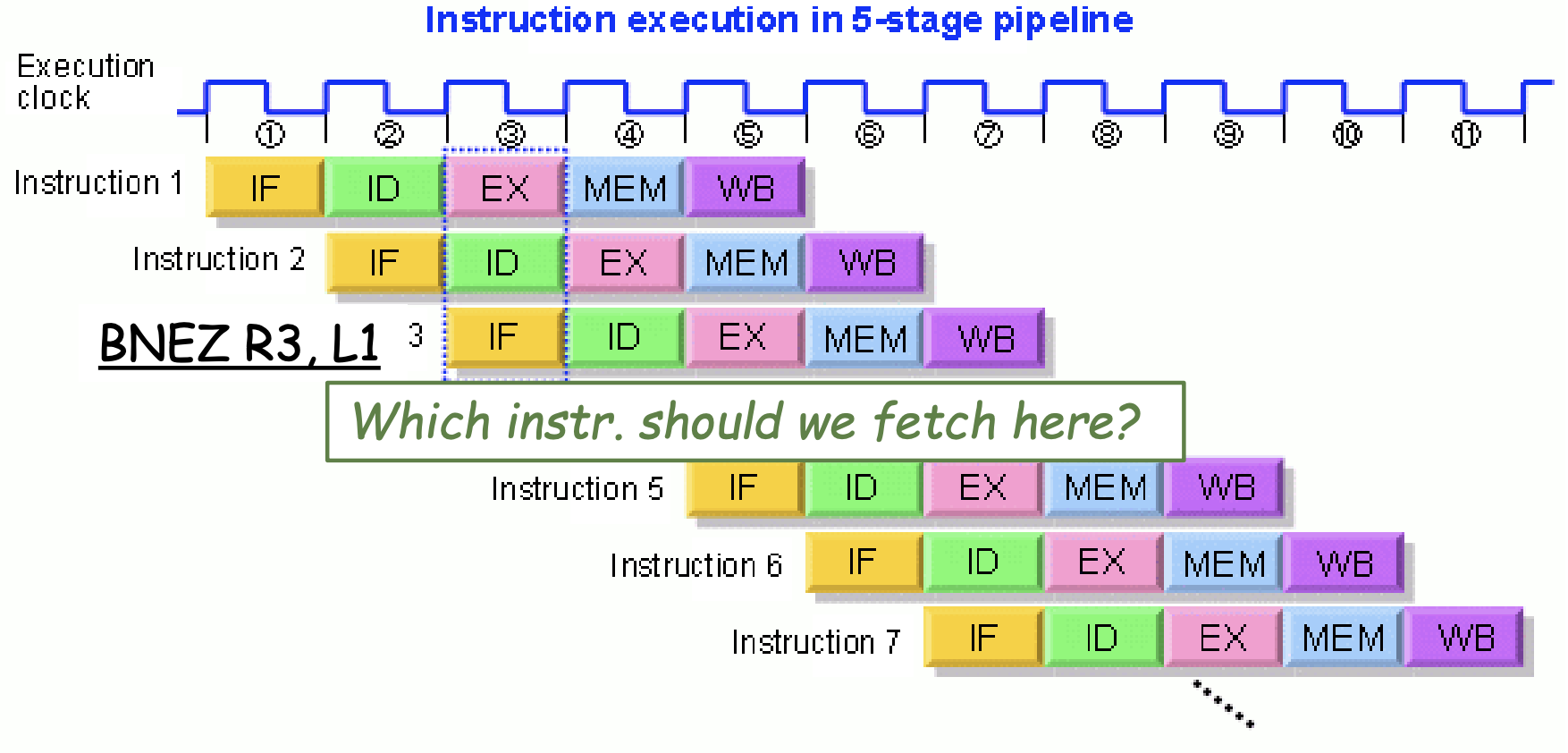

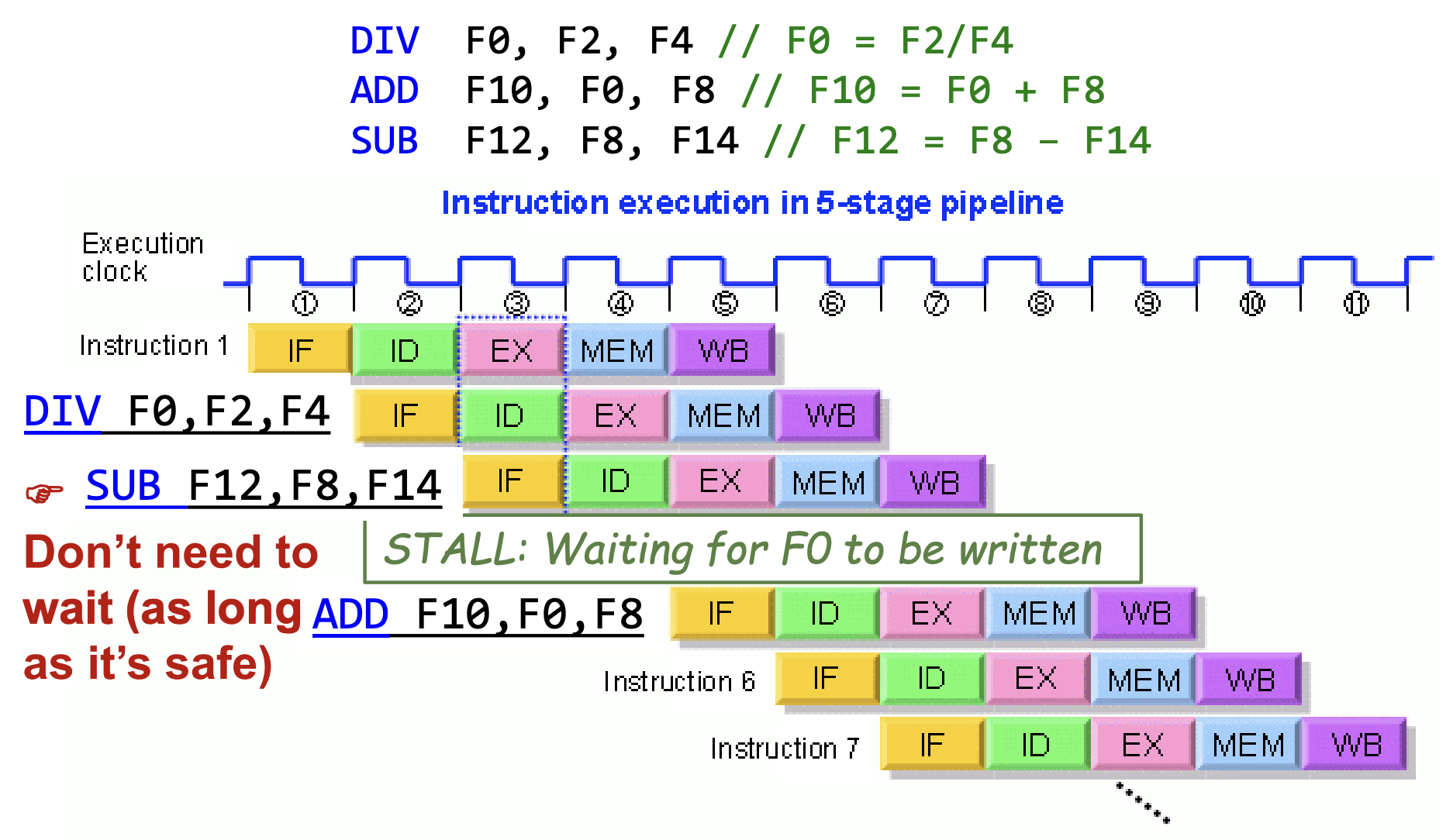

Pipeline and Branch Prediction

Some instructions are dependent on the result of other instruction(control-flow instructions), thus after these control-flow instruction the address that needs to be fetched next is not determined for certain number of cycles in pipelined processor. Generally brench instructions take up 15% to 25% of the code, and since code were having deeper pipeline, superscalar architecture, object oriented, the number of indirect branch increases that necessitate the creation of branch predictor.

Intuitively, branch prediction is done by making prediction for the future based on the history. They uses tables to remember outcome of the previous branches.

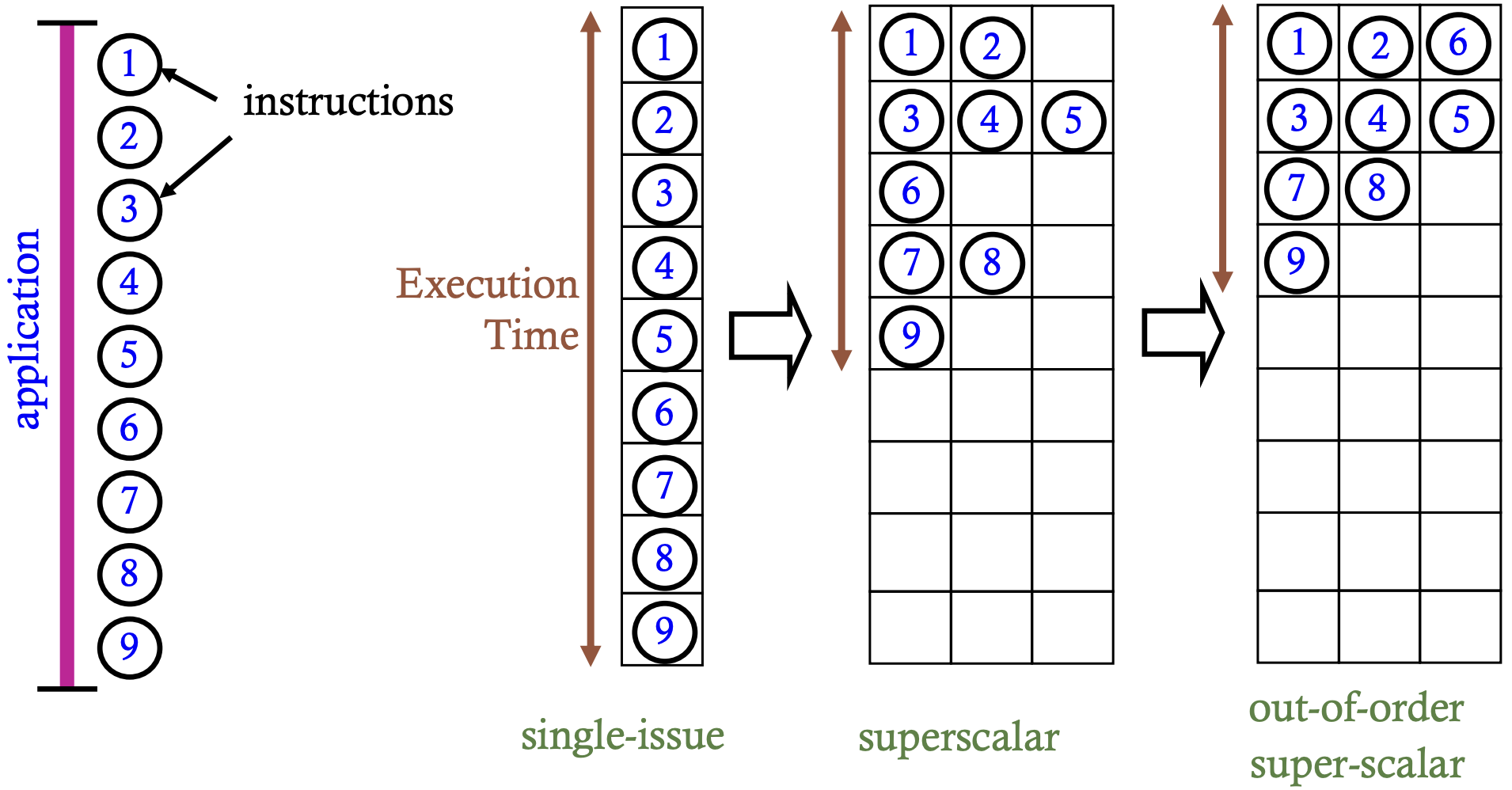

We have now learned pipelining that reduced cpi to 1 but is there way to reduce cpi less than 1?

Instruction-level parallelism:

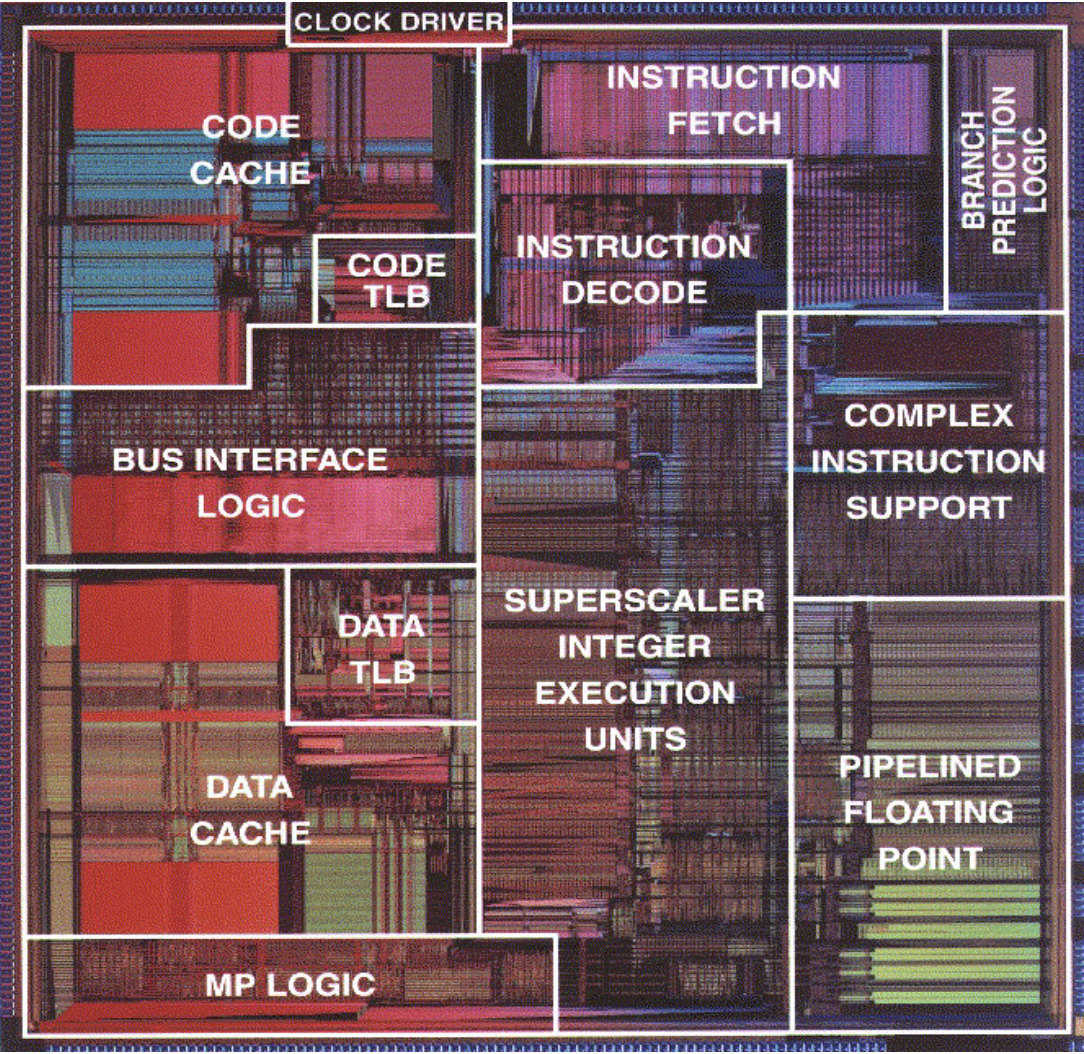

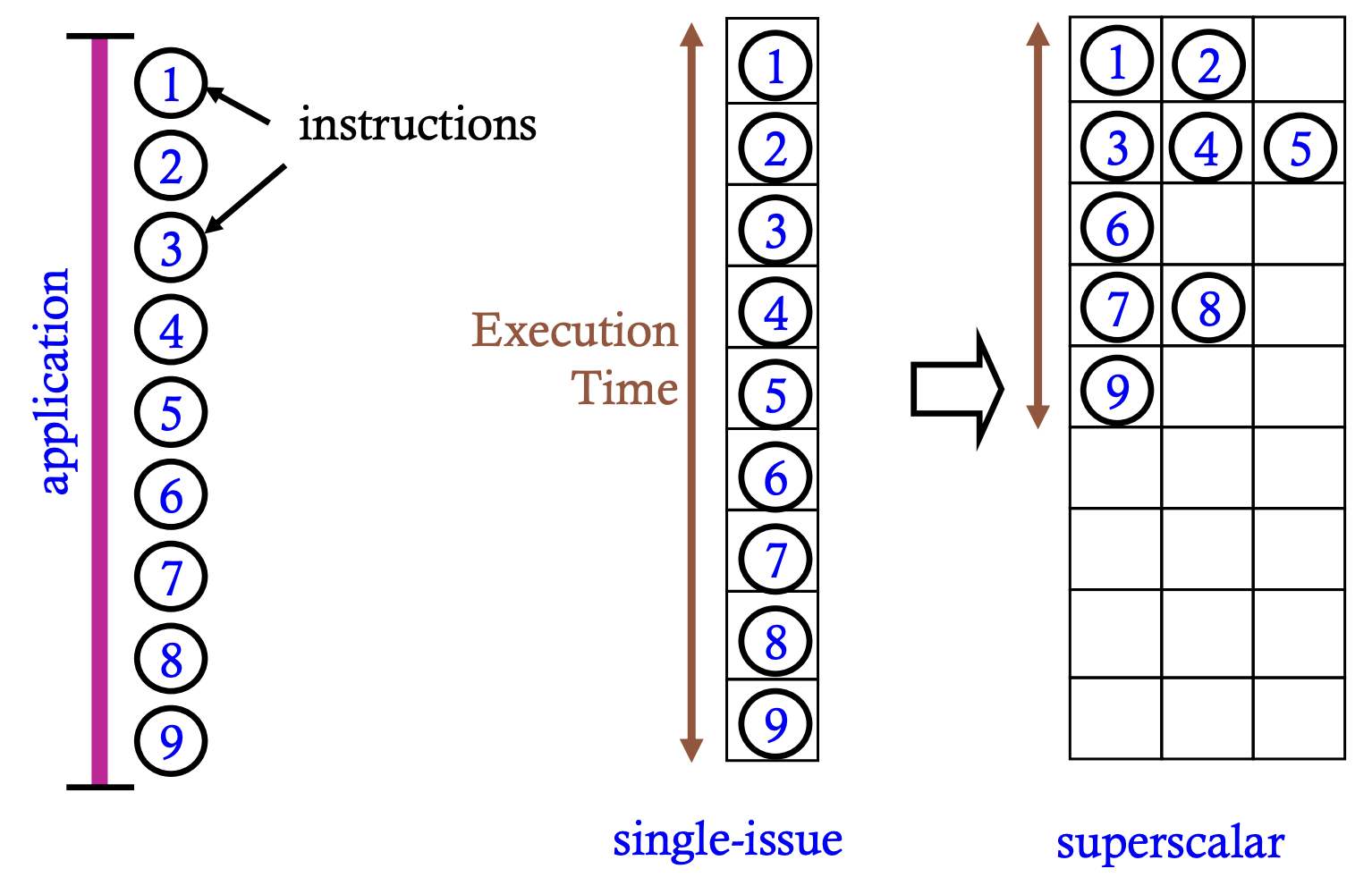

1993 : Intel Pentium

processor has now evloved to fetch and process multiple instruction at the same time by having multiple pipelines. This is known as superscalar.

Instruction-level parallelism is limited because wider out of order superscalar won’t effect the order of execusion. Diminishing returns for the wider superscalar.

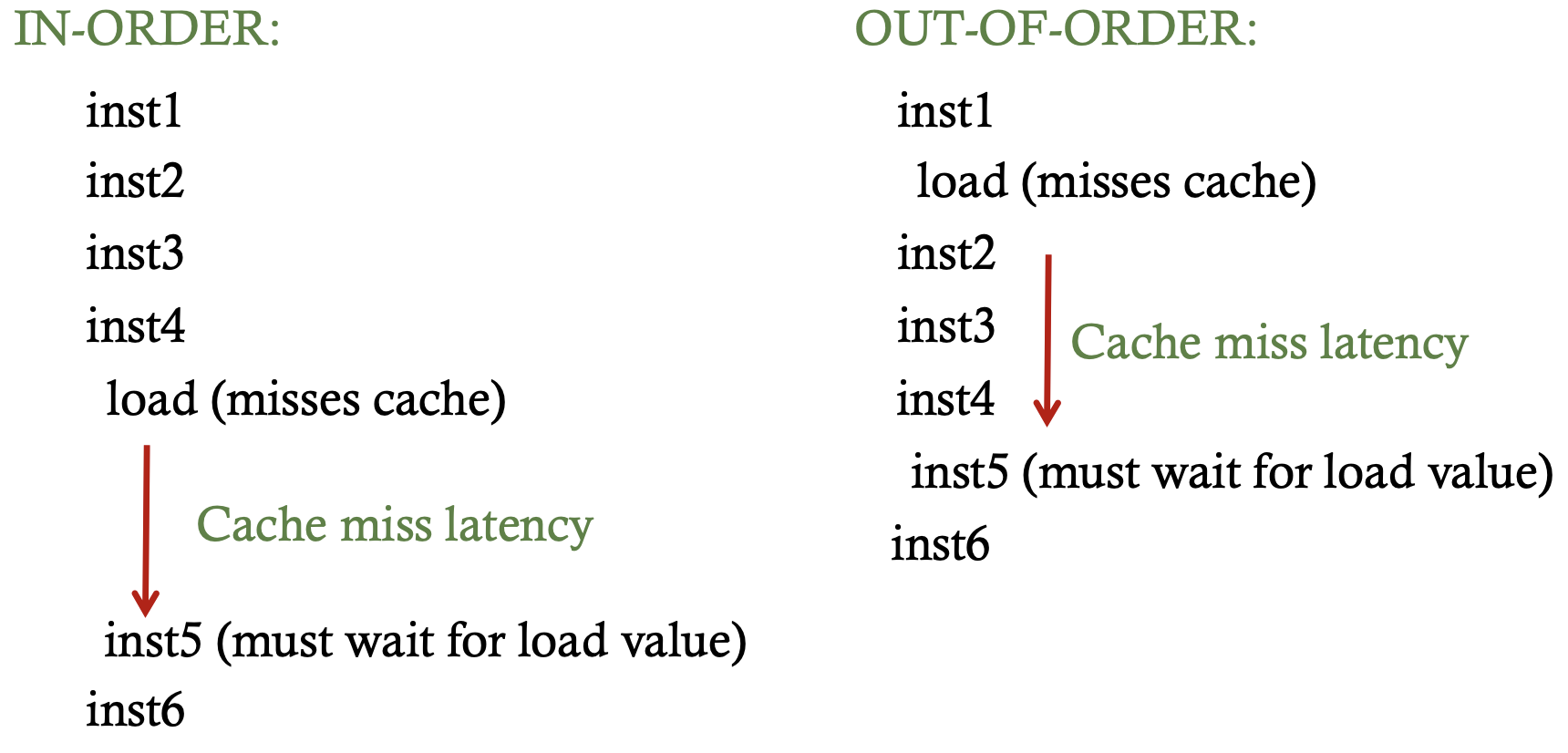

out-of-order execution

According to wikipedia:

in out-of-order execution, a processor executes instructions in an order governed by the availability of input data and execution units,rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently.

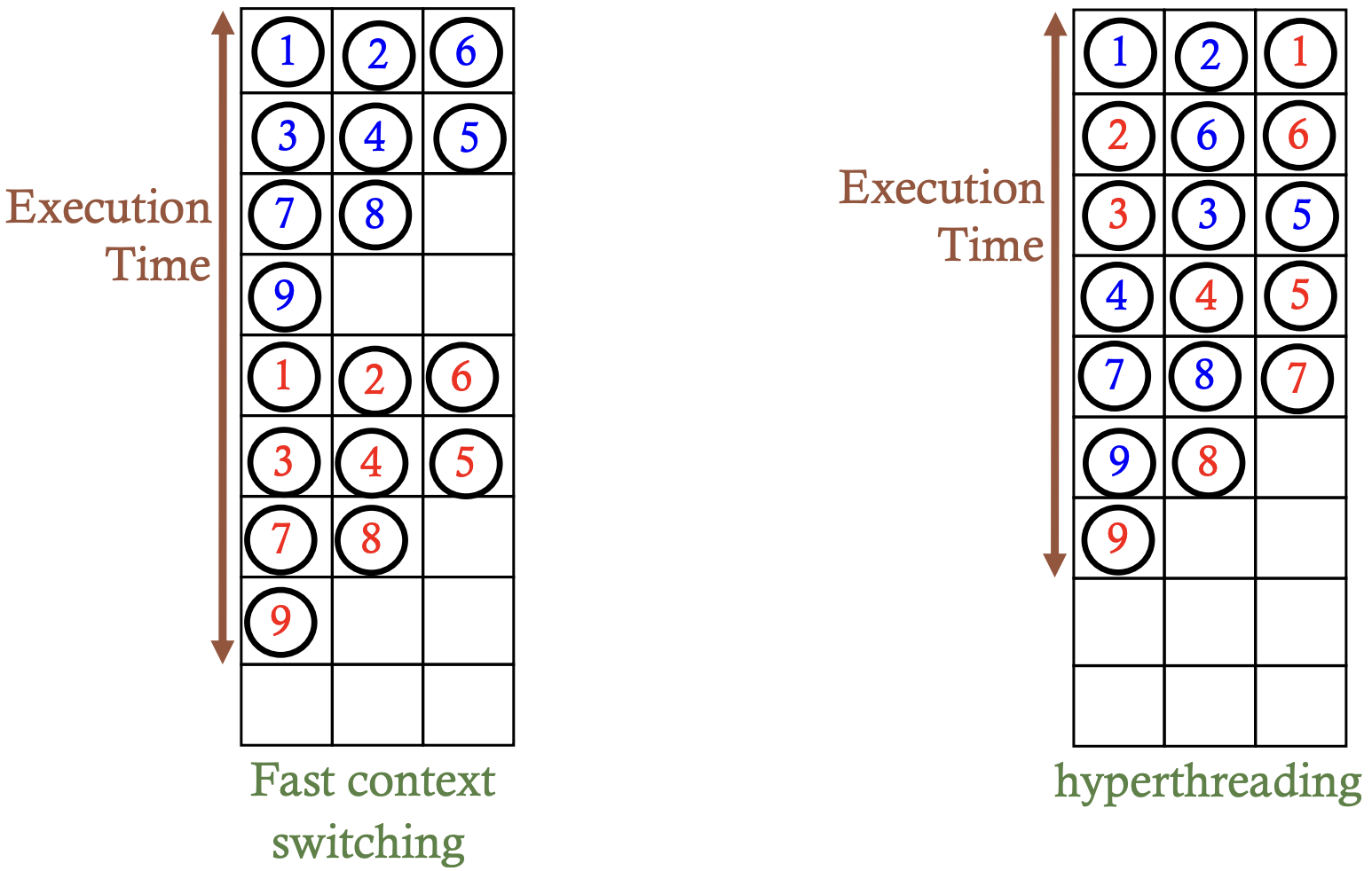

Simultaneous Multithreading(SMT), Hyperthreading

SMT is known to be 20-30% faster than context switching.

Summary of Intel architecture

| year | Processor | Tech | CPI |

|---|---|---|---|

| 1971 | 4004 | No pipeline | n |

| 1985 | 386 | Pipelining, Branch prediction | close to 1 |

| 1993 | Pentium | Superscalar | <1 |

| 1995 | PentiumPro | Out-of-order exec. | «1 |

| 1999 | Pentium III | Deep pipeline | shorter cycle |

| 2000 | Pentium IV | SMT | «<1 |

32-bit to 64-bit Computing

the number indicate the size of the address space. for 32-bit computing 32bit address space is used while 64bit computing uses address space with 64 bit.

Leave a comment